- 您现在的位置:买卖IC网 > Sheet目录3841 > PIC18LF66K80-I/PT (Microchip Technology)MCU PIC ECAN 64KB FLASH 64TQFP

PIC18F66K80 FAMILY

DS39977F-page 154

2010-2012 Microchip Technology Inc.

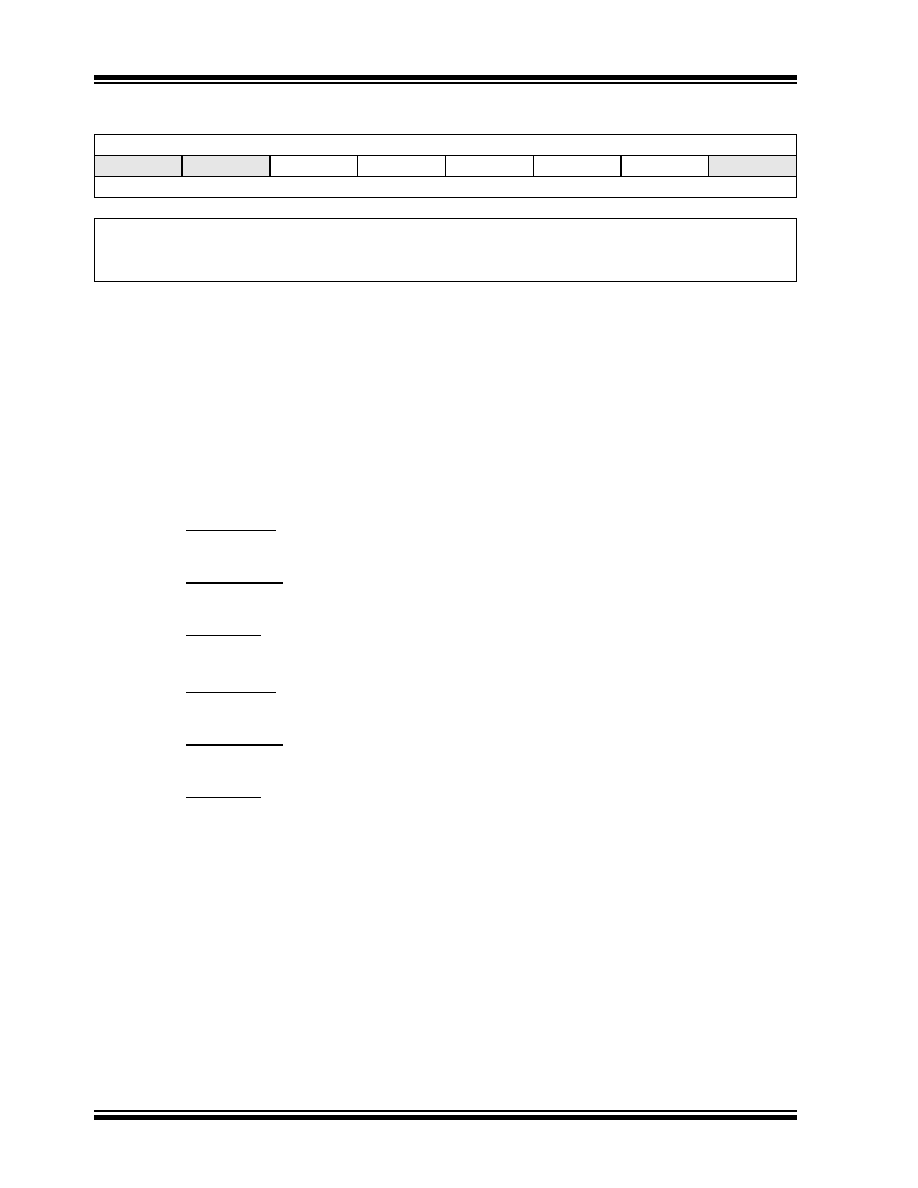

REGISTER 10-6:

PIR3: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 3

U-0

R-0

R/W-0

U-0

—

RC2IF

TX2IF

CTMUIF

CCP2IF

CCP1IF

—

bit 7

bit 0

Legend:

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as ‘0’

-n = Value at POR

‘1’ = Bit is set

‘0’ = Bit is cleared

x = Bit is unknown

bit 7-6

Unimplemented:

Read as ‘0’

bit 5

RC2IF:

EUSARTx Receive Interrupt Flag bit

1

= The EUSARTx receive buffer, RCREG2, is full (cleared when RCREG2 is read)

0

= The EUSARTx receive buffer is empty

bit 4

TX2IF:

EUSARTx Transmit Interrupt Flag bit

1

= The EUSARTx transmit buffer, TXREG2, is empty (cleared when TXREG2 is written)

0

= The EUSARTx transmit buffer is full

bit 3

CTMUIF:

CTMU Interrupt Flag bit

1

= CTMU interrupt occurred (must be cleared in software)

0

= No CTMU interrupt occurred

bit 2

CCP2IF:

CCP2 Interrupt Flag bit

Capture mode:

1

= A TMR1/TMR3 register capture occurred (must be cleared in software)

0

= No TMR1/TMR3 register capture occurred

Compare mode:

1

= A TMR1/TMR3 register compare match occurred (must be cleared in software)

0

= No TMR1/TMR3 register compare match occurred

PWM mode:

Unused in this mode.

bit 1

CCP1IF:

ECCP1 Interrupt Flag bit

Capture mode:

1

= A TMR1/TMR3 register capture occurred (must be cleared in software)

0

= No TMR1/TMR3 register capture occurred

Compare mode:

1

= A TMR1/TMR3 register compare match occurred (must be cleared in software)

0

= No TMR1/TMR3 register compare match occurred

PWM mode:

Unused in this mode.

bit 0

Unimplemented:

Read as ‘0’

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC24FJ64GA308-I/PT

MCU 16BIT 64KB FLASH 80TQFP

PIC18F66K80-I/PT

MCU PIC 64KB FLASH 64TQFP

PIC24FJ64GA104-I/ML

IC PIC MCU FLASH 64KB 44-QFN

PIC32MX250F128B-I/SP

IC MCU 32BIT 128KB FLASH 28-SDIP

PIC18F47J53-I/PT

IC PIC MCU 128KB FLASH 44TQFP

DSPIC30F1010-30I/SP

IC DSPIC MCU/DSP 6K 28DIP

PIC24FJ64GB002-I/ML

IC MCU 16BIT 64KB FLASH 28QFN

52746-1270

CONN FFC 12POS .5MM R/A ZIF SMD

相关代理商/技术参数

PIC18LF66K80T-I/MR

功能描述:8位微控制器 -MCU 64KB FL 4KBRM 16MIPS 12bit ADC CTMU XLP RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18LF66K80T-I/PT

功能描述:8位微控制器 -MCU 64KB FL 4KBRM 16MIPS 12bit ADC CTMU XLP RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18LF6720-I/PT

功能描述:8位微控制器 -MCU 128KB 3840 RAM 52I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18LF6720-I/PT

制造商:Microchip Technology Inc 功能描述:8BIT FLASH MCU 18LF6720 TQFP64

PIC18LF6720-I/PTC01

制造商:Microchip Technology 功能描述:MCU 8-Bit PIC18 PIC RISC 128KB Flash 1.8V/2.5V/3.3V/5V 64-Pin TQFP Tray

PIC18LF6720T-I/PT

功能描述:8位微控制器 -MCU 128KB 3840 RAM 52I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18LF6721-I/PT

功能描述:8位微控制器 -MCU 128kBF 4096RM 40MHz nonoWatt RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18LF6721T-I/PT

功能描述:8位微控制器 -MCU 128kBF 4096RM 40MHz nonoWatt RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT